3D integration

3D options for enhanced integration

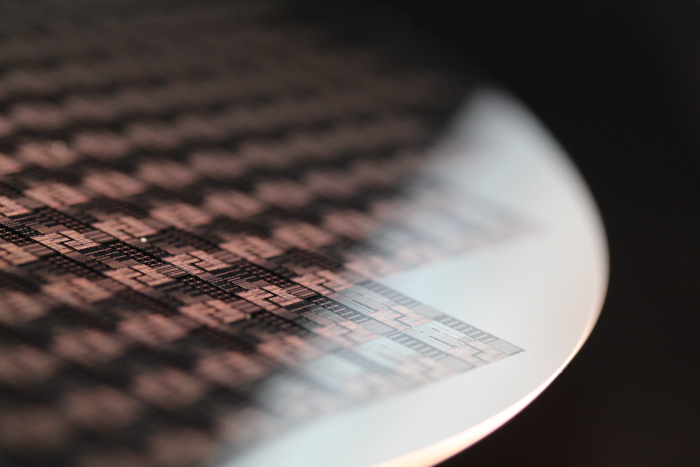

3D integration exploits the third physical dimension to stack functionalities into a small form factor package, delivering high performance, low power and efficient systems. 3D integration is a very relevant solution for the so called ‘more than Moore’ systems by combining heterogeneous technologies in the same package with logic, memory, analogue and RF components and micro electro-mechanical systems. 3D is an alternative to systems on a chip combining several best-in-class semiconductor technologies options for each function.

Electronic designers are constantly looking for creative approaches to deliver more functionality, higher performance and increasingly compact systems. Systems on a chip (SoC) have delivered increasingly complex chips, integrating logic, memory, embedded software, analogue, RF and I/Os on the same die. However, such chips require long and costly development cycles.

Systems in package (SiP) provide an alternative where several dies are assembled in the same package. One of the advantages of SiPs is their modular approach with lower development costs and the opportunity to mix heterogeneous semiconductor technologies. Until recently, SiP relied on conventional wire bonding assembly with limited connection density and sub optimal form factor.

3D stacking provides dramatically denser connectivity thanks to, for instance Through Silicon Vias (TSVs). 3D integration is a significant step forward in system integration and enables system designers to select the best node and silicon technology for each stack.

The FAMES Pilot Line delivers two state-of-the-art 3D options: 3D heterogeneous integration and 3D sequential integration.

Designers can use 3D heterogeneous integration to combine different semiconductor technologies for outstanding performance, small form factor and optimized power consumption. FAMES 3D heterogeneous technologies can thus be used to combine silicon technologies and dies based on III-V or other materials such as organic or glass substrates.

3D heterogeneous integration involves very high accurate die to wafer stacking to create complex More-than-Moore systems interconnected using TSVs, micro-pillars or micro-bumps.

With 3D sequential integration, the tiers of a 3D chip are processed after bonding, meaning that the contact density is no longer limited by mechanical bonding alignment, but by the outstanding accuracy of lithography tools. As a result, an unrivalled contact density is obtained, down to the individual superposed devices (transistors, memory cells etc). However, the processing the top tier must be carefully adjusted to avoid hindering the performance and functionality of the lower ones. This is a challenge tackled by FAMES, thanks to forefront process techniques.

Heterogeneous 3D integration

A novel 3D approach developed by FAMES: Chiplet architecture with very low latency

- TSV : Back-Side Mid-BEOL TSVs

- Cu/SiO2 HB : 5 µm pitch

- Front-Side and Back-Side RDLs

→ Interconnect density can be increased by a factor of up to 100

Sequential 3D integration

FAMES aims to enlarge FD-SOI heterogeneous co-integration with other devices using 3DSI to address new systems and markets:

- Demonstrating 3D sequential integration with increasingly complex circuits;

- • Evaluating opportunities for smart and scaled 3tier-pixels with GaN μLED and RF applications.

See more

- Event

- Press Release

- Event

- Event