OPEN-ACCESS

FAMES Pilot Line Open-Access

The FAMES Pilot Line offers European semiconductor stakeholders from industry, research, and academia access to a unique set of advanced semiconductor technologies, chip design & testing, technology demonstrators and manufacturing capabilities.

This initiative aligns with the goal of the EU Chips Act : boosting the European semiconductor ecosystem and strengthening European technological sovereignty. By giving early access to the FAMES Pilot Line technologies, as they become available, we foster their adoption.

Discover our technologies: FD-SOI, eNVM, RF components, 3D Hybrid Integration and PMIC options

2026 Annual Open-Access Call

Opens:

March 9, 2026

Closes:

May 22, 2026 at 23h59 CET (deadline for submissions)

2026 Open-Access Technology Portfolio

The following technologies are available for the duration of the Open-Access Call period.

Please submit an Open-Access Call User Request form if you would like to gain access to them.

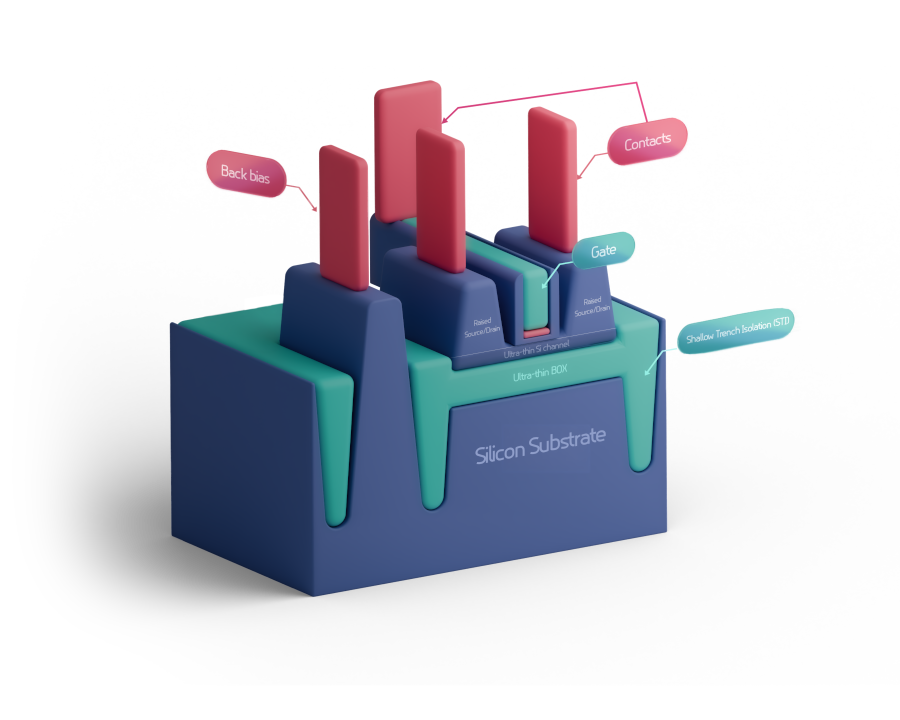

FD-SOI 10nm Pathfinding PDK

Overview

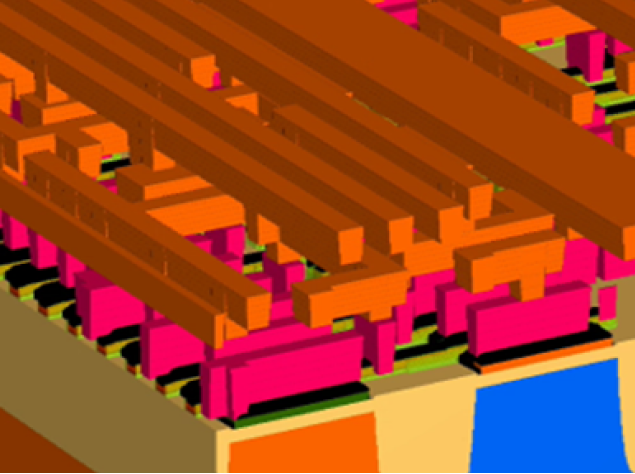

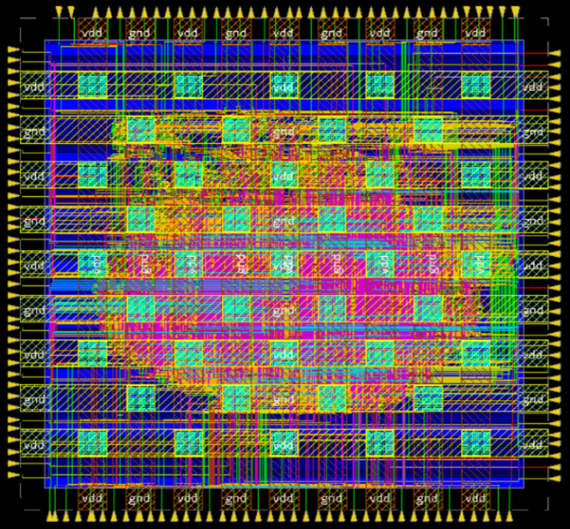

FAMES is currently offering a Pathfinding PDK to evaluate the performance of the 10nm FD-SOI CMOS technology. Based on process and device TCAD simulations and silicon data, this first release allows for assessment of digital circuits. Process assumptions are based on the most recent generations of FD-SOI technology enabling 68nm CPP and 48nm metal pitches. It contains 16 logic standard cell libraries (see below for more detail) with several threshold voltage flavors (multi-Vth), 2 poly-bias options, SPICE models, tools for physical verification and a parasitic extraction tool for post-layout simulations.

Based on virtual advanced FD-SOI technologies, this PDK will allow users to create new design architectures that benefit from Body bias compensation, mechanical stress engineering for both NMOS and PMOS devices, and new routing solutions, among others.

Expected timeline

Release 1, for digital circuits, is available.

Release 2, which will have analog and RF options too, will be available Q1 2027.

Access and technical support

Users may obtain access to FAMES Pathfinding PDKs free of charge by signing an NDA and a Design Kit License Agreement. A collaborative approach will be preferred.

FAMES Pathfinding PDK users will have access to technical support from FAMES experts and the possibility of building and publishing model case studies with one or more FAMES partners.

PDK Specifications and Contents

- Design Rule Manual

- Device library including multi-Vth MOSFET for schematics and layouts

- 4 Vth flavors (SLVT, LVT, RVT, HVT)

- 2 poly-bias options for digital devices + CPP 136nm analog option

- SRAM transistors: pass gate, pull-up and pull-down

- Device model library supporting multi-Vth solutions for SPICE simulation

- Process variability and corner support

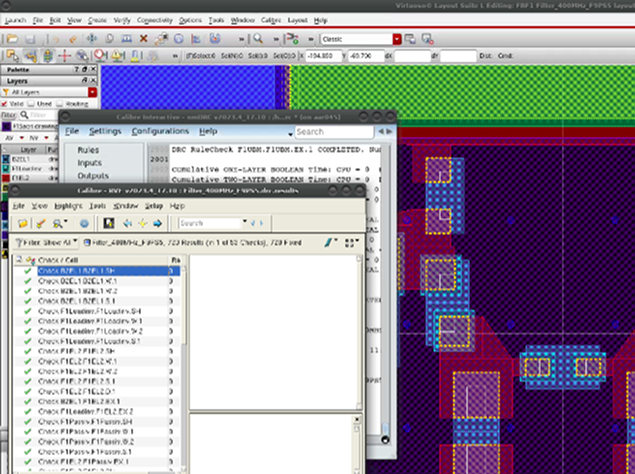

- DRC/LVC deck files for physical verifications

- PEX extraction tool

- 2×8 Digital standard cell libraries : two library families with eight libraries each, one for high density and another for high performance

- SRAM bitcells

- Technological LEF and QRC files

Enabling tools required

- Design/Layout: Virtuoso® Layout Suite (Cadence)

- Electrical Simulation: Xpedition AMS (Siemens EDA),HSPICE® (Synopsys) and Spectre (Cadence)

- Physical Verification (DRC/LVS): Calibre® (Siemens EDA)

- Parasitic Extraction (PEX): StarRC® (Synopsys)

- Place and Route: Innovus® (Cadence)

Credit: CEA-Leti – SEMulator3D®

Credit: CEA-Leti – FIR filter circuit top view

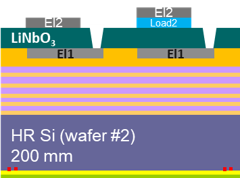

15 GHz LiNbO3 BAW filters

Overview

FAMES has created a 200 mm Solidly Mounted BAW Resonator filter technology platform. This platform offers an opportunity to design and fabricate custom prototype filters that can be integrated on foundry interposers and/or RF-ICs.

FAMES is developing innovative acoustic filter technologies to address the FR3 frequency range (7-24 GHz). This is made possible thanks to high-coupling piezoelectric materials such as lithium niobate.

This innovative BAW-SMR technology will provide highly miniaturized band pass filtering capabilities to RF systems in the FR3 range, and could advantageously replace conventional microwave filters in wireless systems.

Expected timeline

A PDK dedicated to filters intended to operate near a centre frequency of 15 GHz will be available Q2 2026.

Design your specific BAW-SMR filter in time to meet the design freeze planned for end 2026.

Access and technical support

To access the FAMES BAW-SMR filter PDK, Users must sign an NDA and a Design Kit License Agreement (DKLA). The price of R&D samples will depend on the User’s specific RF Filter Design.

FAMES PDK users will have access to technical support from FAMES experts.

PDK Specifications and Contents

- Design Rule Manual

- Device Library including parametric cells for layouts

- Device models for circuit and circuit/electromagnetic coupled simulations

- Process variability support

- DRC check for physical verifications

Technological features

- 200 mm custom technology

- Add-on possible for Wafer Level Thin Film Packaging (WLTFP) of the resonators/filters

- 5 mask levels (9 with the WLTFP option)

If you would like to obtain the WLTFP option, please mention it on the User Request submission form in the comments area.

Enabling tools required

- Analog circuit design: Advanced Design System® (Keysight)

- Layout: Virtuoso® (Cadence)

- Physical verification (DRC): Calibre® (Siemens EDA SW)

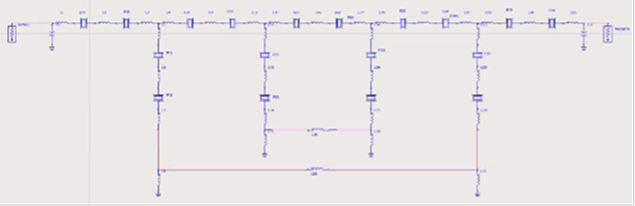

Layout environment illustration. Credit : CEA-Leti – Cadence Virtuoso®; Siemens EDA Calibre®

ADS simulation circuit illustration. Credit: CEA-Leti – Keysight ADS®

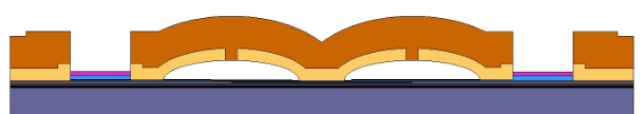

To scale model of a filter cross-section with its thin-film packaging. Credit: CEA-Leti

Schematic of a BAW filter stack @ 15GHz. Credit: CEA-Leti

7-15 GHz AlN/ScAlN RF filters

BAW resonator R&D Services: RF AlN/ScAlN filter (7-15GHz)

Overview

FAMES offers a 200 mm platform of FBAR filters targeting the 7-15 GHz range (lower frequencies are also possible). The platform is based on highly piezoelectric ScAlN films and low resistance multilayer electrodes optimized for high frequencies. This is a pre-release (“beta”) offer allowing Users to evaluate the platform’s potential.

Expected timeline

The PDK for the AlN/ScAlN RF Filter platform is expected Q4/2026.

Users must sign an NDA and a Design Kit License Agreement (DKLA) before gaining access to the PDK. A collaborative approach will be preferred. PDK Users will have access to technical support from FAMES experts.

Description of Services

Evaluation of FR3 ScAlN BAW resonator and filter processes

- RF filter test samples

- Can be manufactured in the 7-15 GHz range.

- Frequencies below 7 GHz are also possible, within certain process variations.

- Test resonator designs

- Test resonators can be manufactured to User specified frequencies.

- For plain resonators, some layouts are available.

- RF filter design support

- Limited device and process design rule guidance available.

- Wafer level characterization (S-parameters) available.

RF Filter Platform

- ScxAl1-xN (x=0.2, 0.3) films.

- Low sheet resistance multilayer electrodes.

- Restrictions in film thicknesses/frequency ranges. Assessment per customer request.

- Ion beam trimming for thickness & frequency accuracy presently limited to the end of the process; in-line trimming will be available in 2027.

Estimated price and fabrication time

- RF resonator/filter test samples take 16-20 weeks to be produced.

- Characterisation time estimated at 4-6 weeks.

- Price will vary as a function of the test samples and services requested.

- Estimated delivery dates will take into account the process line load.

High frequency BAW resonator test structures. VTT Technical Research Centre of Finland.

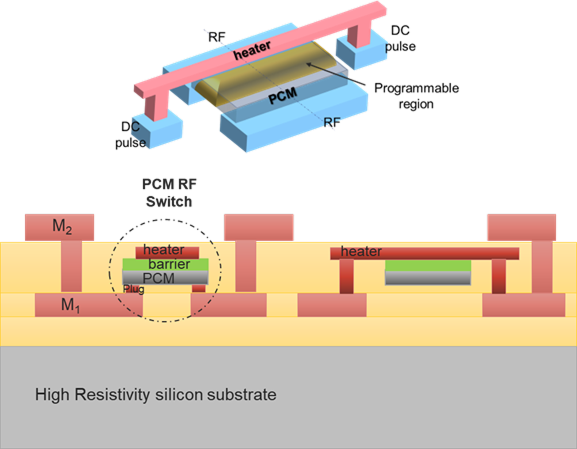

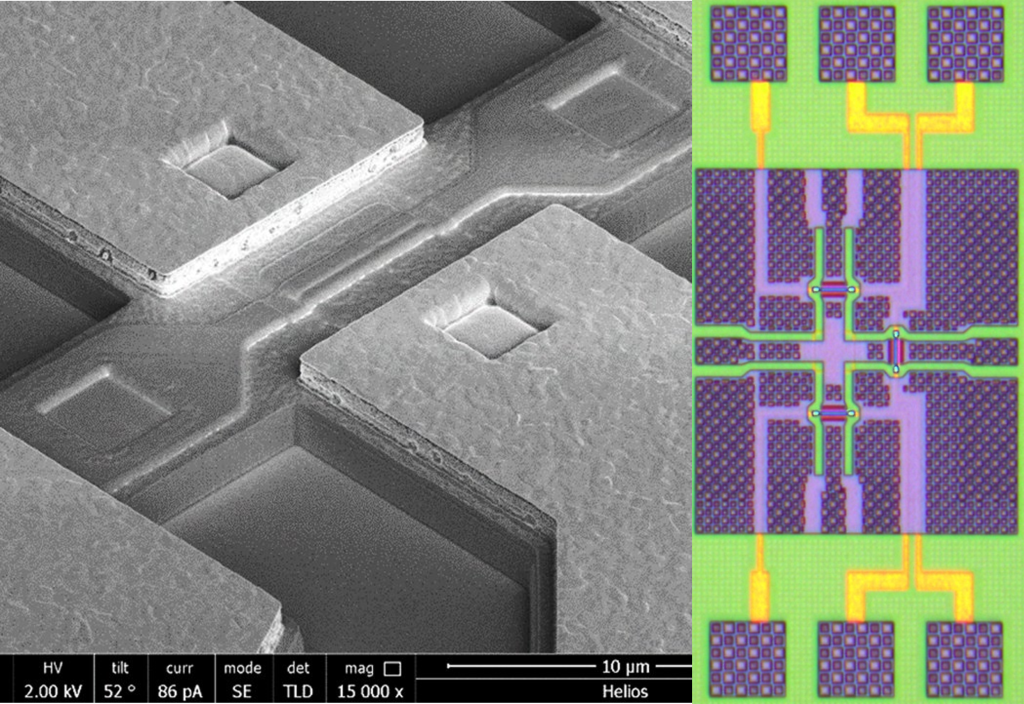

PCM RF switch demonstrators

PDK to access an RF Switch demonstrator based on a Phase Change Material

Overview

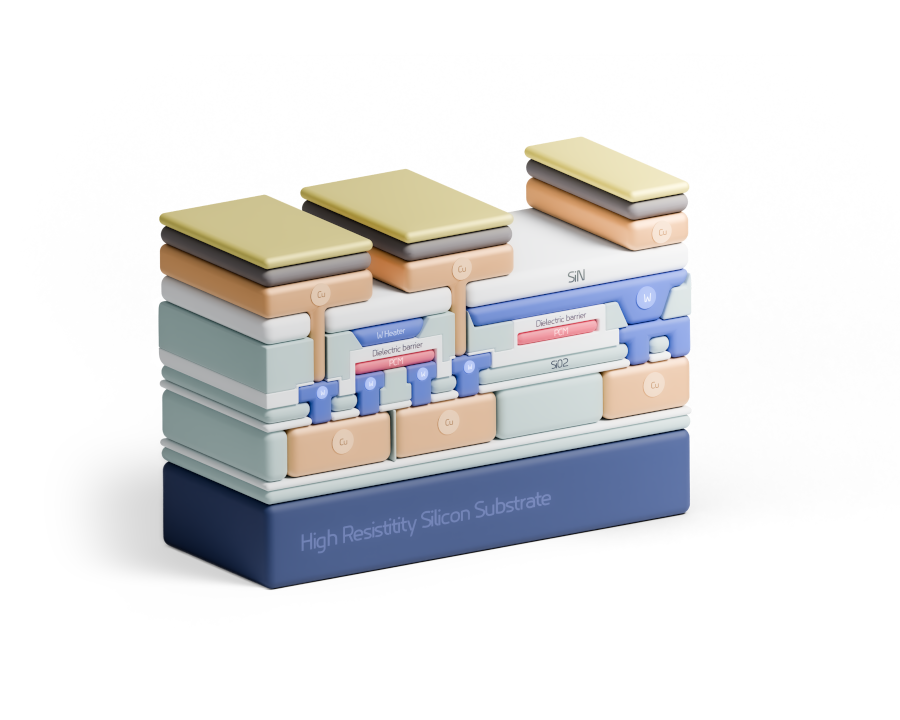

FAMES is integrating, onto a 300 mm technology platform, RF Switches based on PCM (Phase-change chalcogenide materials), having a Figure of Merit (FOM = RON*COFF) < 10 fs. This technology can be positioned within a CMOS Back-End-of-Line (BEOL) to enrich the technological offer of semiconductor foundries.

A PDK (Release1) will give access to silicon by way of an MPW, allowing Users to design specific PCM RF switch demonstrators and obtain R&D samples of those designs.

Expected timeline

A first release of the PDK is expected by Q4 2026 and will allow Users to implement specific designs on a high resistivity silicon substrate.

Users interested in this technology should respond to the 2026 FAMES Open-Access Call.

Access and technical support

To access the FAMES PDK for PCM RF switch Users must sign an NDA and a Design Kit License Agreement (DKLA). The price of R&D samples will depend on the User’s specific RF Switch design.

FAMES PDK Users will have access to technical support from FAMES experts.

PDK Specifications and Contents

- Design Rule Manual

- Device library including PCM core cell for schematics and layouts

- Device model for simulation

- DRC for physical verification

Technological features

- 300 mm High Resistivity Silicon Technology substrate

- 2 Metal layers + 1 resistive Metal layer (heater) + PCM layer

Enabling tools required

- Layout: Virtuoso® Layout Suite (Cadence)

- Physical verification (DRC): Calibre® (Siemens EDA SW)

Other related R&D Services

- Design and layout expertise

- Circuit testing

- Expertise to analyse test results

If you would like to obtain any of these additional services, please mention it on the User request Submission Form in the comments area.

Schematic of a PCM RF Switch Release 1. Credit: CEA-Leti

Optical microscope image of a Single- Pole Triple-Throw device based on PCM RF switch technology. Credit: CEA-Leti

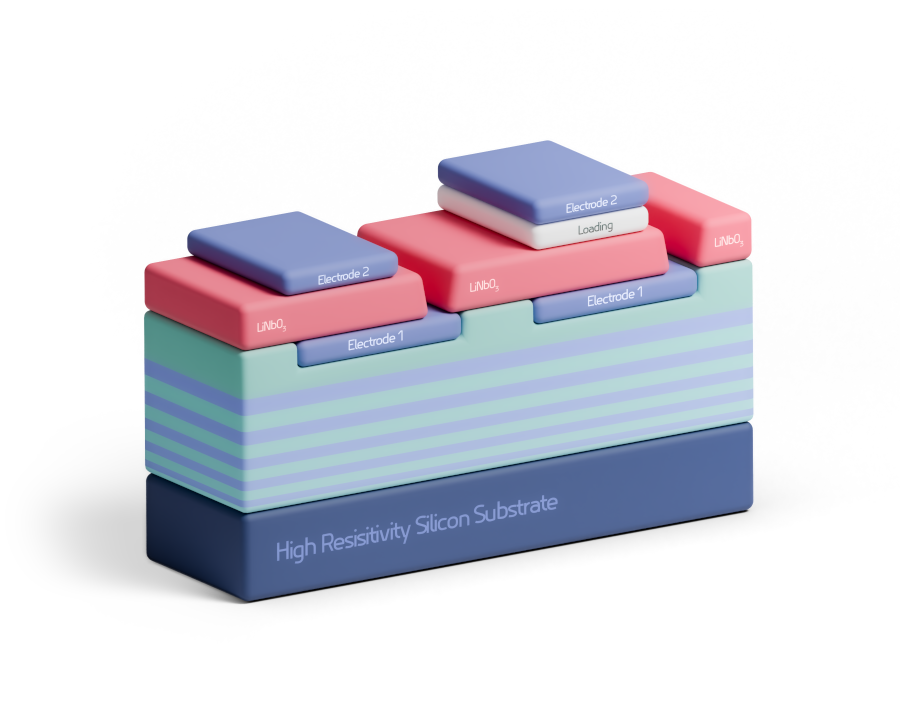

PMIC options: Magnetics on Silicon

Overview

Powering integrated circuits using traditional Point of Load DC-DC converters is becoming a major concern because of the significant losses and parasitics that occur in the interconnect for the Power Delivery Network (PDN). This has led to a transition to granular arrays of integrated voltage regulators that deliver vertical power to ICs with minimal PDN losses and parasitics. A key enabler of this transition to Integrated Power has been the move from bulky inductors to miniaturized magnetics on silicon enabled by the use of power converters operating at frequencies in the range 10 to 100 MHz.

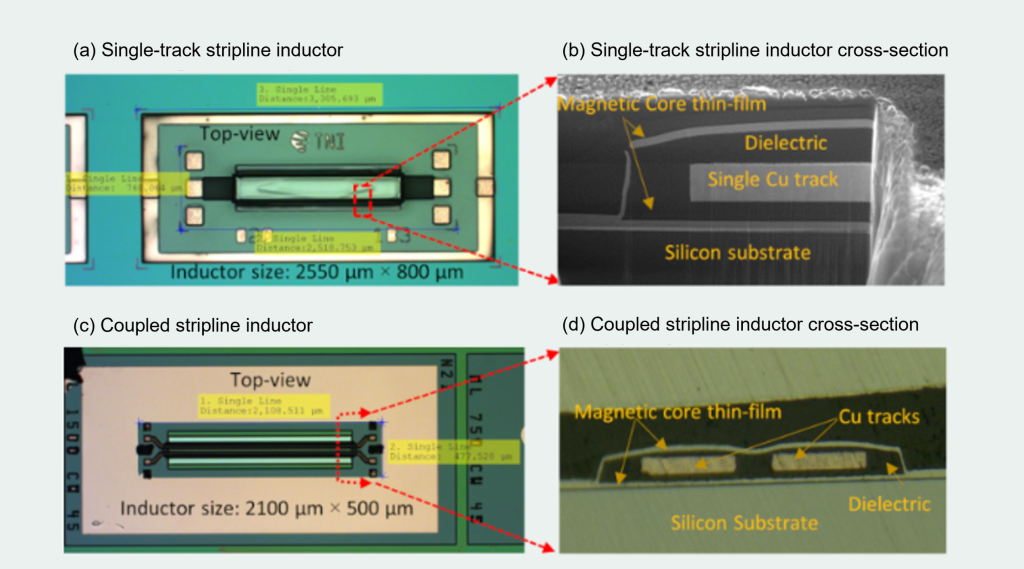

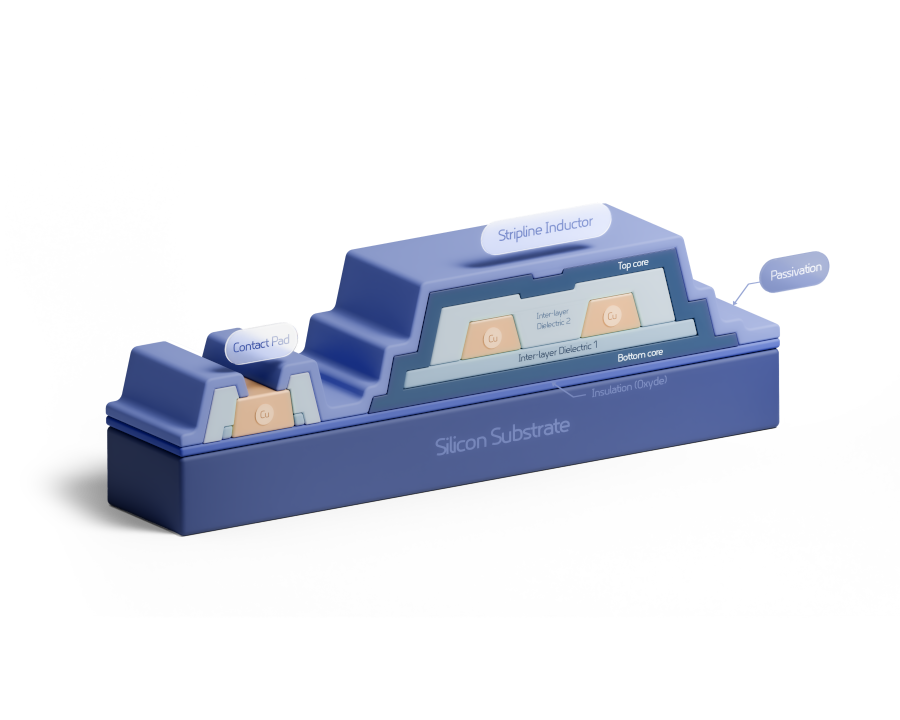

Within the FAMES Pilot Line, Tyndall National Institute is developing its integrated magnetics on silicon technology for application with customized Power Management Integrated Circuits (PMIC) and high-density trench capacitors. The technology, known as MagIC (making magnetics disappear onto silicon), can deliver a stripline micro-inductor (see Fig. 1a-b) and micro-transformer (shown as a coupled inductor in Fig. 1c-d) with a footprint of less than 2550 µm × 800 µm and a substrate thickness of 100 to 525 µm.

Inductances of 3 to 5 nH can be provided with Q > 8 for operation in the 10 to 50 MHz frequency range.

Expected timeline

Samples of these micro-inductors and micro-transformers will be accessible at the end of 2026/start of 2027. Interested Users should respond to this 2026 FAMES Open-Access Call.

Access and technical support

To receive samples of the FAMES Magnetics-on-Silicon, Users will be required to sign an NDA.

Users who gain access to FAMES’s Magnetics-on-Silicon will have access to technical support from Tyndall experts.

Inductor Specifications

- Inductor Parameters:

- Single Strip-line Inductor: Inductance = 3 – 5 nH; Q > 8; Operating Frequency: 10 – 50 MHz

- Coupled Strip-line Inductor: 3 – 5 nH; Coupling Coefficient = 0.5 – 0.7

- Inductor die thickness including substrate: max. 600 µm

- Substrate choices: Silicon and SOI

- Inductor footprint: max. 2550 µm × 800 µm (Including the bond pads and surrounding mechanical support area)

- Test Data and Deliverables for Samples Provided:

- Measurement Data:

- Inductance, DC Resistance (DCR), small-signal measured AC Quality Factor (Q) and saturation current (Isat)

- Inductors bumped or copper plate exposure for flip-chip assembly

- Device model for SPICE simulation

- Inductors bumped for with Flip-chip assembly

Other related R&D Services

- DC-DC converter assembly, including inductors, with User PMICs and capacitors

- Converter Circuit testing

If you would like to obtain any of these additional services, please mention it on the User Request submission form in the comments area.

(a) Top view of a Tyndall-fabricated Single-track stripline micro-inductor on silicon substrate, (b) Cross-section of a part of the single-track micro-inductor showing a single Cu track surrounded by the thin-film magnetic core, (c) Top view of a Tyndall-fabricated coupled stripline micro-inductor on silicon substrate, and (d) Cross-section of the coupled micro-inductor showing two Cu tracks surrounded by a thin-film magnetic core.

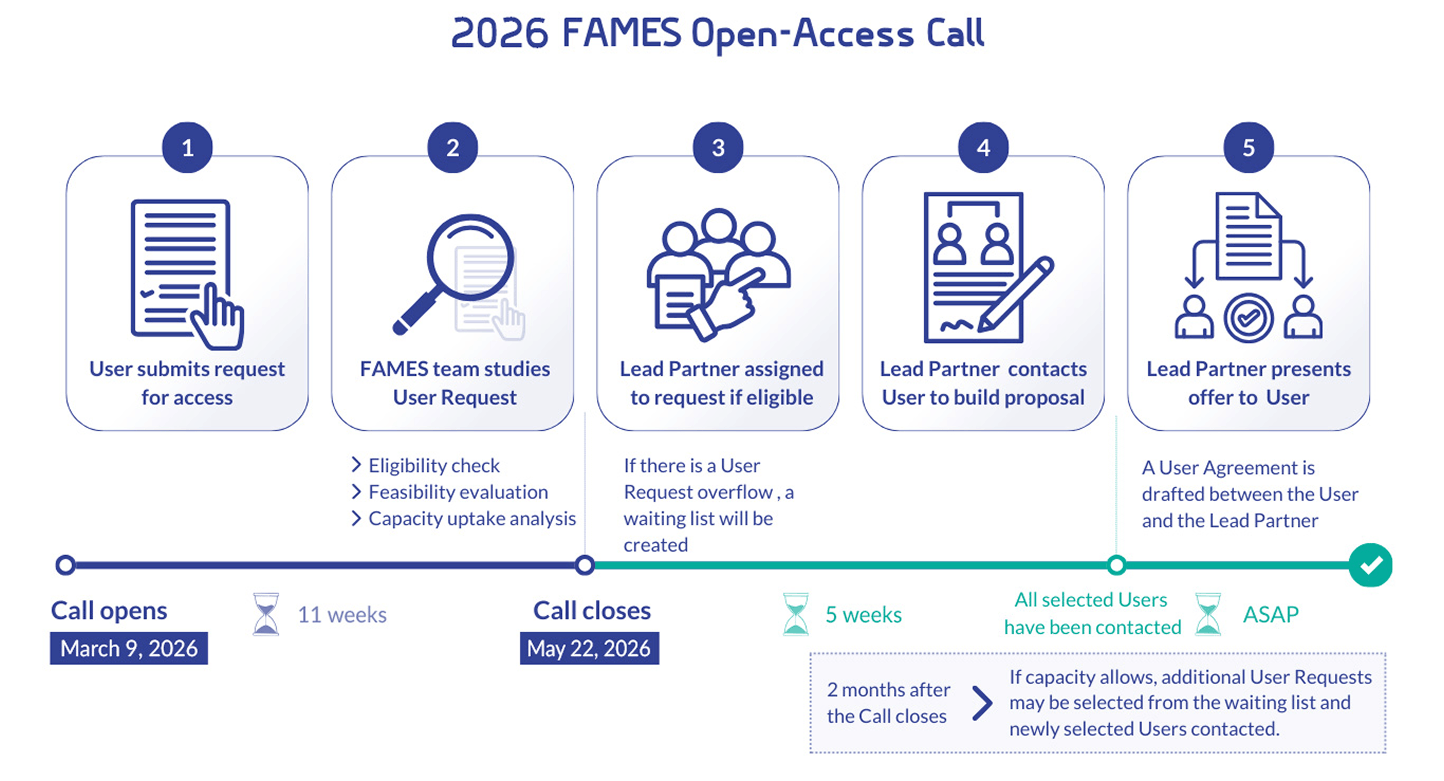

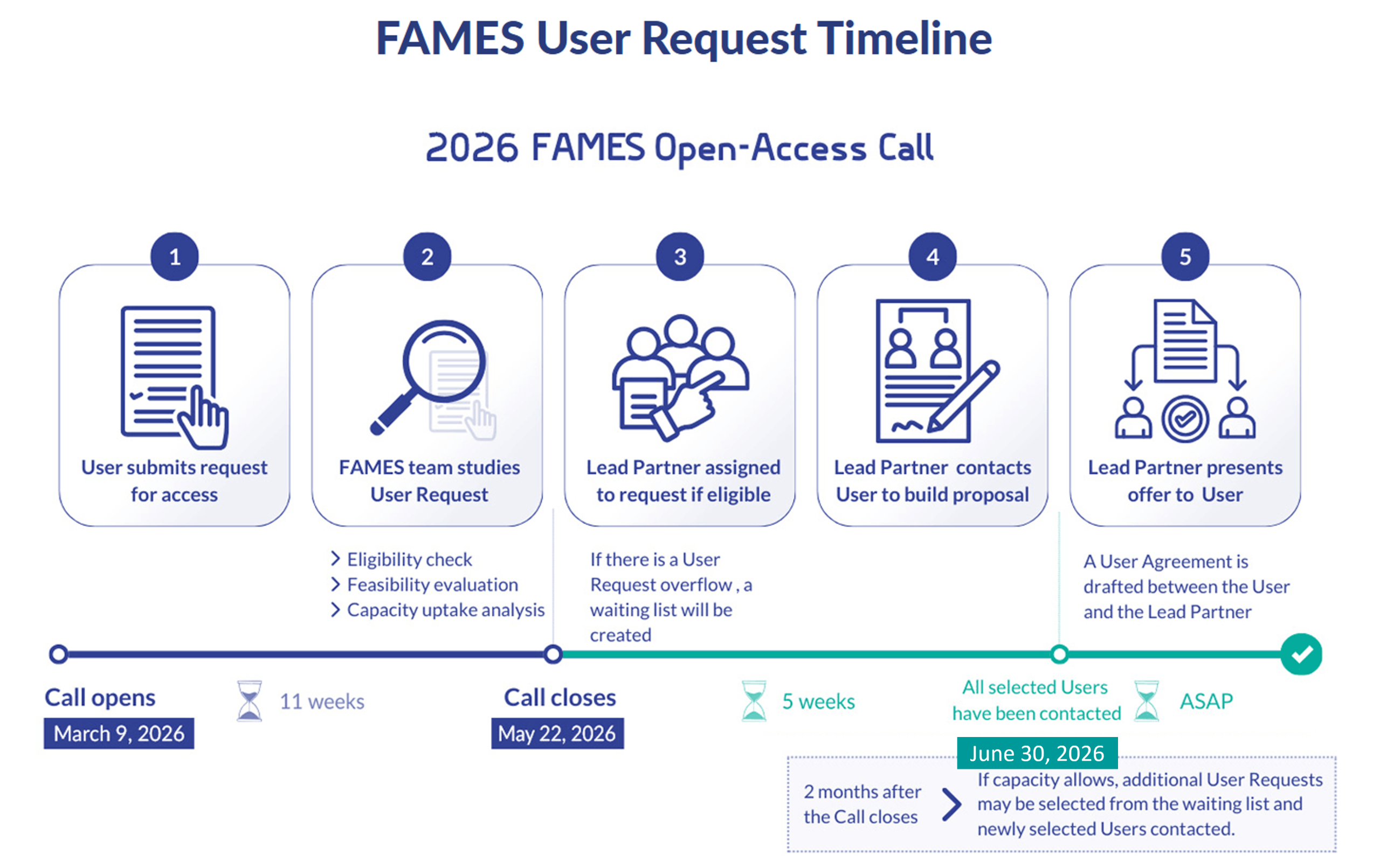

FAMES User Request Timeline

Spontaneous User Request

The FAMES Pilot Line is currently accepting Spontaneous User Requests, for Users whose needs go beyond the 2026 Open-Access Call.

How does it work?

The use of the Pilot Line is subject to fair, reasonable and non-discriminatory terms and conditions.

All access requests submitted by Potential Users will be evaluated for eligibility, technical feasibility and pilot line capacity uptake.

In the event that too many eligible requests are received compared to the capacity of the line, ranking criteria will be used to prioritize the different User Requests. The eligibility and ranking criteria are listed in the dedicated section of the User Guidelines and Procedures document.

Who is eligible?

Once you submit a Spontaneous User Request to access the FAMES Pilot Line,

The Open Access Committee (OAC) will evaluate its eligibility and, if it is eligible, appoint a Lead Partner to your request.

The Lead Partner will:

- Contact you for a first exchange, to clearly understand your needs. An NDA may be signed at this time for this purpose.

- Co-construct an R&D User Project with you, corresponding to your needs.

For more details, please refer to the User Guidelines and Procedures.

User Guidelines and Procedures

User Guidelines and Procedures – full text

Technological portfolio

User Access Governance and Process Flowcharts

User Request Selection and Ranking Criteria

Pricing and Estimated Leadtimes

Multi-partner projects

IP and Know-How

Statistical tracking of User Projects

Personal Data Protection

Submission forms content

Confidentiality

User Access Contact

Download the guidelines

Frequently Asked Questions

Eligibility refers to the regulations of the European Commission and the participating States concerning the contribution of companies and research institutions to the European semiconductor ecosystem. The Eligibility criteria are listed in Section 5 of the User Guidelines and Procedures.

Please consult the FAMES User Request timeline.

In the event of a User Request overflow, some User Requests will be put on a waiting list. Two months after the submission deadline of the FAMES-Open-Access Call, the waiting list will be reviewed by the Open Access Committee and new User Requests may be selected if the Pilot Line capacity allows it. At this point, Users will be notified of the status of their Request. If their Request cannot be accepted this time around, and depending on the technology requested, it may be possible to resubmit a Request during the following FAMES-Open-Access Call.

FAMES Open-Access Calls will take place every year from 2025 to 2028. They will open in March and close in May.

The PDK is accessible for free but requires signing an NDA and a Design Kit License Agreement (DKLA).

The Open Access Chairperson will be glad to answer any questions you may have regarding the submission form and the FAMES technologies.