NEWS & RESULTS

News and highlights

- Technology

- Technology

- Training

FAMES Newsletter

Subscribe to our newsletter to keep up to date with the latest news and achievements of the FAMES project.

The newsletter is released every trimester.

FAMES publications

Articles in Journal

Ber K., Wiśniewski P., Modeling of RRAM based PUF: a case study, Solid-State Electronics, DOI: https://doi.org/10.1016/j.sse.2025.109267

Wiśniewski P., Jeżak P., Małkowski A., Kądziela A., Krzemiński J., Mroczyński R., Investigation of compliance current effect on resistive switching properties in Ag/SiOx/Cr RRAM devices, Solid-State Electronics, DOI: https://doi.org/10.1016/j.sse.2025.109288

Articles in Journal

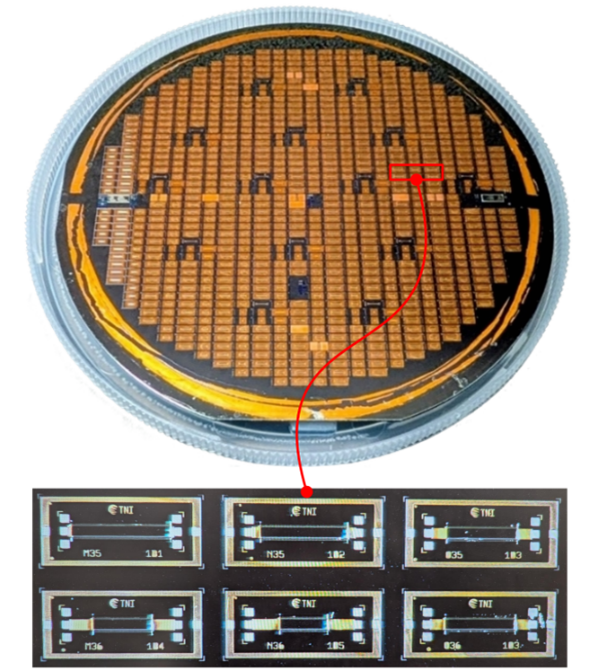

Martínez A., Márquez C., Lorenzo F., Gutiérrez F., Caño-García M., Ávila J., Carlos Galdón Gil J., Ortega Lopez R., Navarro C., Donetti L., Gámiz F., Wafer-Scale Demonstration of BEOL-Compatible Ambipolar MoS2 Devices Enabled by Plasma-Enhanced Atomic Layer Deposition, ACS Applied Materials & Interfaces, DOI: 10.1021/acsami.5c12014

Tran, N. P., Tran, N., Milesi, F., Le, V. H., Zouknak, L. D., Dezest, P., … & Fenouillet-Beranger, C. Toward Full Relaxation of Ssoi Substrates for Pfet Device Fabrication. P. and Rodriguez, Philippe and Brunet, Laurent and Duriez, B. and Cyrille, MC. and Fenouillet-Beranger, C., Toward Full Relaxation of Ssoi Substrates for Pfet Device Fabrication. doi: 10.1016/j.sse.2025.109196

Zouknak, L. M., Le, V. H., Tran, N. P., Milesi, F., Hartmann, J. M., Jarjayes, S., … & Fenouillet-Beranger, C. (2025). Nanoscale SOI strain engineering: STRASS-enabled local stress optimization. Solid-State Electronics, 109215. doi: 10.1016/j.sse.2025.109215

Bazzi, A., Levices, H., Talatchian, P., Badets, F., & Hutin, L. (2025). Ising-inspired invertible adders using coupled phase-locked CMOS ring oscillators. Physical Review Applied, 24(1), 014004. doi: https://doi.org/10.1103/8xc2-vkk3

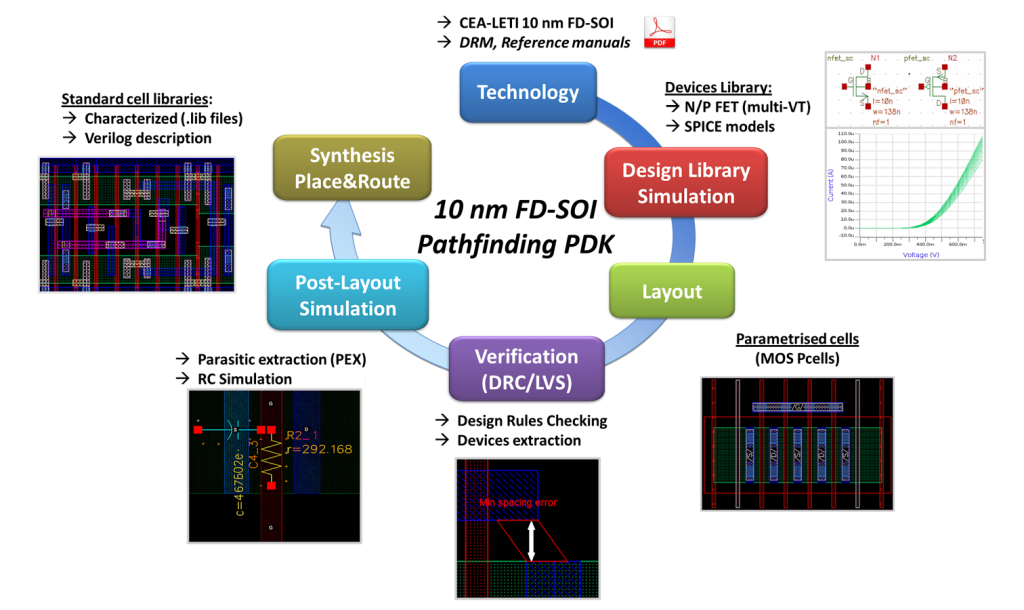

Fenouillet-Beranger, C., Rozeau, O., Chouk, R., Cueto, O., Royet, A. S., Charbonneau, M., … & Noguet, D. Pursuing the Fd-Soi Roadmap Down to 10-7nm Nodes for High Energy Efficient, Low Power and Rf/Mmwave Applications. doi: 10.2139/ssrn.5316840

Barge, D., Gallard, M., Hartmann, J. M., Fournel, F., Loup, V., Mazen, F., … & Servant, F. 300 Mm Ssoi Engineering with Ultra Thin Box. Available at SSRN 5316841: doi.org/10.2139/ssrn.5316841

Marquez, C., Gity, F., Galdon, J. C., Martinez, A., Salazar, N., Ansari, L., … & Gamiz, F. (2025). On the Enhanced p‐Type Performance of Back‐Gated WS2 Devices. Advanced Electronic Materials, 2500079. doi: https://doi.org/10.1002/aelm.202500079

Lèquepeys, JR., Noguet, D., Paing, B. et al. Europe’s pilot line on fully depleted silicon-on-insulator technology (FAMES). Nat Rev Electr Eng 2, 77–78 (2025). https://doi.org/10.1038/s44287-025-00144-y

Milesi, F., Rodriguez, P., Zouknakl, L.D.M. et al. Process challenges of the STRASS technique to increase the electron mobility in advanced FD-SOI nMOSFETs. MRS Advances 10, 174–178 (2025). https://doi.org/10.1557/s43580-025-01148-4

Bonnet D., Cottart K., Hirtzlin T., Januel T., Dalgaty T., Vianello E., Querlioz D., Bayesian continual learning and forgetting in neural networks, Nature Communications volume 16, Article number: 9614 (2025), DOI: https://doi.org/10.1038/s41467-025-64601-w

Publications in Conference proceeding/workshop

Bosch D. , Vandendaele W., Diallo E-A., Royet A-S., Albouy A., Opprecht M., Darras F-X., Benevent V., Maillard P., Adami O., Ribotta M., Kerdilès S., Gassilloud R., Garros x. and Batude P., High Performance 2.5V n&p 400°C SOI MOSFETs: a Breakthrough for versatile 3D Sequential Integration, IEDM. doi: 10.1109/IEDM50572.2025.11353514.

Lehninger D., Zhang T., Reinig P., Barbot J., Opprecht M., Kerdiles S., Grenouillet L., Seidel K., Lederer M., Enhanced Ferroelectricity in Hf0.5Zr0.5O2 Thin Films by NLA at Intermediate Laser Energy Density, 2025 International Conference on IC Design and Technology (ICICDT), Lecce, Italy, 2025, pp. 61-64. doi: 10.1109/ICICDT65192.2025.11078051

Szekrényes, Z., Le, V. H., Bellanger, P., Badeeb, L., Éles, B., Faragó, A. I., … & Laurent, N. (2025, May). In-line Raman spectroscopy for semiconductors strain engineering and control: Topic/Category AM: Advanced Metrology. In 2025 36th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC) (pp. 1-4). IEEE. doi: 10.1109/ASMC64512.2025.11010779

Frutuoso, T. M., Vandendaele, W., Bond, A., Bringuier, F., Lapras, V., Cyrille, M. C., … & Garros, B. D. X. (2025, March). Fast CV MSM Technique for Comprehensive Analysis of Bulk Trapping in Low-K Carbon-Doped Dielectrics. In 2025 IEEE International Reliability Physics Symposium (IRPS) (pp. 1-7). IEEE. doi: 10.1109/IRPS48204.2025.10983765

Persson, K. M., Eskelinen, P., Kaatranen, O., & Kilpi, O. P. (2025, June). ITO Contact Optimization for Enhancement Mode BEOL MOSFETs. In 2025 Device Research Conference (DRC) (pp. i-ii). IEEE. doi: 10.1109/DRC66027.2025.11105747

C. Fenouillet-Beranger et al., Ultra-Thin-Body and Buried Oxide FD-SOI next generation nodes and eNVM technologies for advanced IC design, 2025 IEEE 28th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Lyon, France, 2025, pp. 105-114. doi: 10.1109/DDECS63720.2025.11006678

Grampeix H., Cabaret T., Lespiaux J., Gergaud P., Gauthier N., Rodriguez P.,, Influence of Dopant and Si:B Cap on Ni(Pt)-Based Silicidation of SiGe:B for Next Generation PMOS FDSOI Devices, https://ieeexplore.ieee.org/document/11072894

Zarudniev M., Ouvry L., MassonG., Paviot A., Dehos C., Courouve P., Dual-Mode Wideband Receiver Operating with Frequency Modulated Impulse Radar Waveform, 2025 IEEE Radar Conference, DOI: 10.1109/RadarConf2559087.2025.11205075

Publications in Conference proceeding/workshop

Jagosz, J., Willeke, L., Gerke, N., Becher, M. J., Plate, P., Kostka, A., … & Bock, C. (2024). Wafer‐Scale Demonstration of Polycrystalline MoS2 Growth on 200 mm Glass and SiO2/Si Substrates by Plasma‐Enhanced Atomic Layer Deposition. Advanced Materials Technologies, 9(22), 2400492. doi: 10.1002/admt.202400492

Kanyandekwe, J., Hartmann, J. M., Lespiaux, J., Marion, T., Saidi, L., Lapras, V., … & Glorieux, O. (2024). Selective Epitaxy of Tensile, Highly Doped SiP for Planar NMOS FD-SOI Devices. ECS Transactions, 114(2), 253. doi: 10.1149/11402.0253ecst

Lespiaux, J., Kanyandekwe, J., Marion, T., Saidi, L., Lapras, V., Bond, A., … & Hartmann, J. M. (2024). Selective Epitaxial Growth of SiGe (: B) for Advanced p-Type Fd-SOI. ECS Transactions, 114(2), 271. doi: 10.1149/11402.0271ecst

Boujnah, A., Cueto, O., Jaud, M. A., Martinie, S., Nallet, F., Fenouillet-Beranger, C., & Rozeau, O. (2024, September). DTCO of advanced FDSOI CMOS technology by process emulation. In 2024 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) (pp. 01-04). IEEE. doi: 10.1109/SISPAD62626.2024.10733323

Royet, A. S., Chouk, R., Cueto, O., Kanyandekwe, J., Lapras, V., Jaud, M. A., … & Rozeau, O. (2024, September). Calibration Insights of Phosphorus Diffusion Model for NMOS FDSOI: Pathway to Advanced Technology Nodes. In 2024 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) (pp. 1-4). IEEE. doi: 10.1109/SISPAD62626.2024.10733008

Jarjayes, S., Brunet, L., & Rodriguez, P. (2024, April). Analysis of the key parameters of box creep process for advanced FDSOI devices. In 2024 25th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE) (pp. 1-4). IEEE. doi: 10.1109/EuroSimE60745.2024.10491442

Rodriguez-Fano, M., Pedini, J. M., Cadot, S., Grampeix, H., Magis, T., Laulagnet, F., … & Barraud, S. (2024, September). Comparative study of ALD MoS 2 on high-k dielectrics for the fabrication of nanowire FETs. In 2024 IEEE European Solid-State Electronics Research Conference (ESSERC) (pp. 129-132). IEEE. doi: 10.1149/11402.0271ecst

D. Bosch et al., Breakthrough Processes for Si CMOS Devices with BEOL Compatibility for 3D Sequential Integrated more than Moore Analog Applications, 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631398.

J. Lugo-Alvarez et al., First Radio-Frequency Circuits Fabricated in Top-Tier of a Full 3D Sequential Integration Process at mmW for 5G Applications, 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631483.

Grampeix, H., Cabaret, T., Kanyandekwe, J., Gauthier, N., Gergaud, P., & Rodriguez, P. Silicidation of Next Generation of FD-SOI Devices: Effect of P Doping Level in epitaxial Si: P Films.

Events

- Event

- Event

- Event

Press releases

- Press Release

- Press Release

- Press Release